In-situ power for RF and power electronics

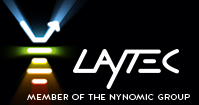

GaN/Si, GaN/SiC and SiC/SiC based devices and related MOCVD processes currently gain increasing interest due to the expected growth rates of the power electronics markets. Recently, at CS ManTech 2015, Yole has forecasted [1]: “2020 exhibits a projected market size for GaN devices of almost $600m (approximately 580,000 x 6” wafers)“ and “SiC device business in 2020 …will exceed $400m”. [Source: Hong Lin of Yole, in Proceedings of CS ManTech 2015] Following this trend, LayTec has further customized its in-situ metrology products for these processes and materials. help our customers to fully exploit the intrinsic advantages offered by wide-bandgap materials (described in Fig. 1) and to manufacture competitive devices with high-yield and cost-efficient processes.

Fig. 1: Summary of Si, SiC and GaN material properties with respect to power electronics applications according to A. Brown, PhD thesis 2015, Glasgow University

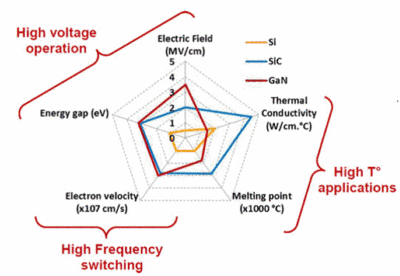

Our in-situ metrology systems are powerful tools in your hand: they provide you with real-time information on what is happening in your deposition system. Tight control of process conditions for every layer in every wafer enables you to optimize your growth processes and achieve the best device performance and uniformity.

LayTec's in-situ metrology provides the following measurements:

- Reflectance at 3 wavelengths for monitoring of growth rate and morphology (EpiTT and EpiCurve®TT product families)

- Wafer surface temperature (EpiTT and EpiCurve®TT product families)

- Wafer curvature for strain management of layer stacks (EpiCurve®TT)

- Reflectance Anisotropy Spectroscopy (RAS) for III-V surface and interface analysis in the R&D stage (EpiRAS®TT)

You will find a detailed overview of our products for electronic device manufacturing in our Electronics Brochure

Here are some further application examples:

Accurate wafer temperature for GaN/Si power electronics with Pyro 400

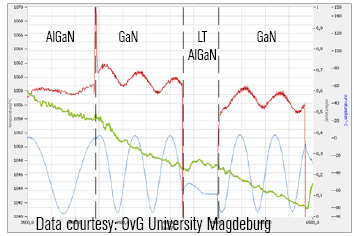

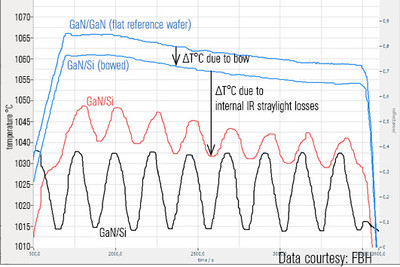

Temperature measurements during MOCVD growth of GaN-on-silicon (GaN/Si) divices is rather challenging. Theoretically, conventional infra-red (IR) pyrometry should be sufficiently because the silicon substrate is IR absorbing in the full range of relevant growth temperatures. However, one artifact makes the feed-back control difficult and prohibits precise statistical process control in industrial applications. Fig. 1 shows this phenomenon: when GaN is grown, the temperature signal (red) starts oscillating by ±2 K.

Fig. 1: GaN/Si template run for creating a compressively pre-strained buffer (as can be seen in the curvature data): red - temperature, green - curvature, blue - reflectance (950 nm)

We searched for a solution together with our partners at Otto-von-Guericke University of Magdeburg (Prof. Armin Dadgar and his team) and FBH (Dr. Frank Brunner) and found out that, no matter how perfect the IR pyrometer is, these oscillations are inevitable. They are caused by a complex interaction between two effects: the IR transparent GaN/AlGaN strain-engineering and the defect reducing buffer structure on the one side, and, on the other side, the thermal IR radiation out of the silicon wafer that passes through the grown structure. Our solution was to use a pyrometry wavelength range in which the complex buffer layer structure Si/AlGaN/GaN/LT-AlGaN/GaN is not "visible" for the pyrometer.

Hence, we took LayTec's ultra-violet (UV) pyrometer Pyro 400, which was developed some years ago for GaN-on-sapphire growth in LED industry. The results are demonstrated in Fig. 2:

Fig. 2: Overgrowth of template of Fig.1 with GaN in a planetary G3 reactor: blue - UV pyrometry, red - IR pyrometry, black - reflectance (950 nm).

Temperature of the GaN buffer measured by Pyro 400 (lower blue curve) is completely free of Fabry-Perot oscillations. The IR temperature (red) shows again oscillations, but, which is even more essential, is also downshifted by -15 K from the true temperature of its GaN surface!

The same wafer as in Fig. 1 was transferred to a reactor at FBH with two in-situ tools: Pyro 400 for UV pyrometry and EpiCurve®TT for IR pyrometry (950 nm emissivity corrected), reflectance as well as curvature measurements. The UV pyrometer (Fig. 2 - blue) gives a very stable wafer temperature signal without oscillations during GaN growth. Measurements on a reference GaN/GaN wafer in the same run (not shown here) verified that both IR pyrometer and Pyro 400 are well calibrated and give exactly the same temperature on an ideally flat and smooth GaN/GaN wafer. Fig. 2 also shows UV pyrometry measurements on the basically flat GaN/GaN wafer. The true GaN surface temperature of the GaN/Si template wafer is ~5 K lower than that of the flat GaN/GaN wafer due to the ~100 km-1 convex bow of the Si template measured by EpiCurve®TT.

Furthermore, it became clear: the remaining oscillations in the IR pyrometry signal (red) are not the most important artifact. Due to interactions of the thermal IR radiation with the internal structure of the GaN/Si buffer, there is an additional downshift in this signal by about 15K! This effect we attribute to the fact that the thermal IR radiation coming out of the silicon loses its intensity while passing the relaxation area close to the Si/GaN interface. These internal straylight losses depend on the Fabry-Perot resonance situation with the total GaN thickness and, therefore, also contribute to the IR temperature oscillations.

Although scientific papers with a detailed root-cause analysis are still in the pipeline and will be publish later this year, we are publishing a rough outline of these results now because of their importance for the power electronics industry. For more information please contact info@laytec.de.

Expanded nk database and advanced analysis for GaN/SiC-4H HEMTs

RF power transistors like HEMTs based on AlGaN/GaN or InAlN/GaN combine high electron mobility and high critical electric field strength. Their nearly three orders of magnitude lower specific on-resistance (theoretical value) compared to silicon based devices could enable an at least 10-fold reduction of power losses, device size and cost. Typically, the best performance is reached on semi-insulating silicon carbide (SiC). However, the MOCVD growth of the related AlGaN and AlInGaN structures on large SiC-4H wafers needs complex growth recipes for strain management and tight statistical process control (SPC) for high process yields. For this technology, LayTec has expanded its high-temperature nk database and implemented additional real-time analysis routines to feed SPC systems with highly accurate in-situ data. Fig. 1 gives an example:

Fig. 1: AlN buffer growth on SiC-4H in a three-step high-temperature process. The 405 nm reflectance data is highly accurate due to auto-calibration to the true SiC-4H substrate temperature measured in-situ by Pyro 400 (blue - measured, red - fitted reflectance). The fit gives the thickness dAlN=73.2±0.5 nm. Data provided by confidential customer.

The initial AlN growth on SiC-6H is performed at very high wafer temperature (measured by Pyro 400 at ±0.5 K accuracy) and with a sophisticated three-temperature process. This ensures significant defect reduction for the subsequent HEMT growth. Despite the varying wafer temperature in this AlN buffer growth process, the latest real-time analysis function library of LayTec's EpiNet software allows our tools to reach ±0.5 nm accuracy in real-time AlN film thickness measurement. This has been achieved by tightly correlating the absolute SiC-4H wafer temperature with high accuracy SiC-4H and AlN nk optical data and implementing new analysis algorithms that separate reflectance changes caused by temperature ramping from the AlN growth effects.

For further information please ask info@laytec.de.

Mitsubishi Electric Corp. uses in-situ monitoring for crack-free GaN-on-Si HEMTs

The main challenge of GaN based HEMT growth on Si is the lattice mismatch between GaN and AlGaN that causes a high tensile stress and often leads to cracks. Mr. Atsushi Era of Mitsubishi Electric Corporation reported recently about growth of crack-free low-bowing GaN-on-Si HEMTs. [1] To improve the breakdown voltage and power added efficiency, his team grows the GaN buffer layer doped with Fe (GaN:Fe). Mr. Era uses LayTec's EpiCurve® TT to monitor surface roughness, growth rate and wafer bowing.

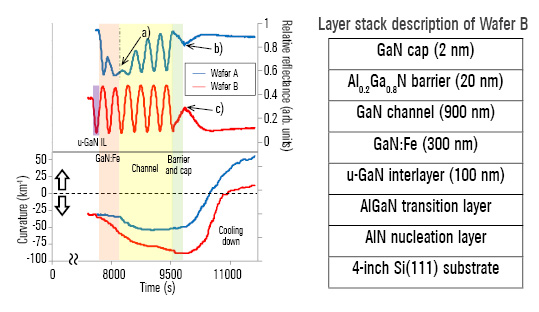

Fig. 1: Left part: In-situ measurements with EpiCurve® TT: Reflectance at 950 nm and curvature data during the growth of Wafers A and B. Right part: Layer stack description of Wafer B.

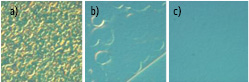

Fig. 1 shows reflectance and curvature measurements during growth of 2 wafers A (blue) and B (red). The reflectance of Wafer A has a clear slump during the GaN:Fe growth, which indicates a rough surface of GaN:Fe layer. The compressive stress during the GaN growth of wafer A is obviously insufficient to compensate the tensile stress during cooling down. The result is a wafer bow of 40.4 μm in size and a crack over the whole area of Wafer A. The respective AFM (atomic force microscopy) images of surface morphologies (a) and (b) in Fig. 2 confirm this:

Fig 2: AFM images of surface morphologies: (a) - wafer A directly after GaN:Fe growth, (b) - finished wafer A, (c) - finished wafer B. (correlate to a, b, c in Fig. 1)

To suppress 3D island growth in the GaN:Fe, Wafer B is grown with a 100 nm thick undoped GaN interlayer (u-GaN IL) prior to GaN:Fe growth. The reflectance of Wafer B in Fig. 1 shows no slump, which indicates that the GaN:Fe layer grows nicely in 2D mode. The compressive stress is well balanced and the wafer bow is finally suppressed to 15.2 μm, so that Wafer B is nearly flat after down-cooling. Its smooth, crack-free surface is confirmed by AFM in Fig. 2(c). Furthermore, the electron transfer characteristics of a device fabricated on wafer B exhibits ideal pinch-off behavior.

[1] A. Era et al. Growth of crack-free GaN on Si HEMTs with Fe-doped GaN using un-doped GaN interlayer, ICSCRM proceedings (2015)

Examples of HEMT growth before and after optimization

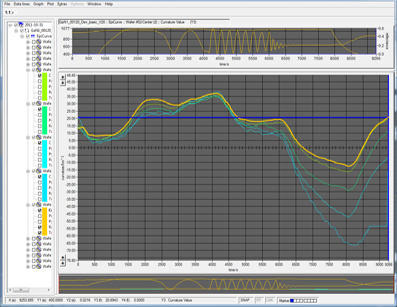

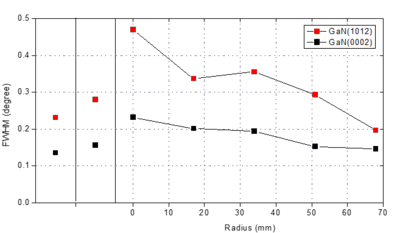

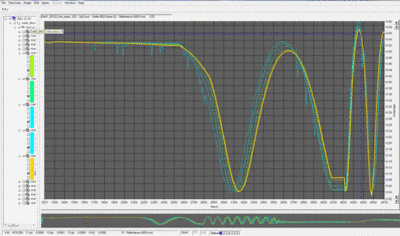

The following example of our industrial customer demonstrates the affect of in-situ monitoring on the final device quality. Real-time in-situ data were used to optimize the growth of high-electron-mobility transistors (HEMTs) on 150 mm Si. Fig. 1 shows in-situ reflectance measured on several points of a wafer (coded in different colors) before growth optimization. It is obvious that the wafer is not homogeneious, which is proved by the X-ray diffraction (XRD) results in Fig. 2.

Fig. 1: In-situ reflectance data of non-optimized HEMT growth.

Fig. 2: XRD results of the non-optimized HEMT growth presented in Fig. 1.

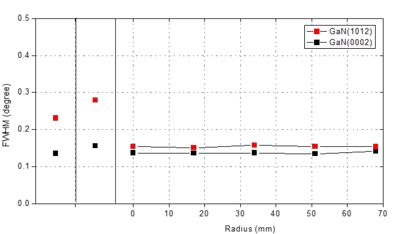

LayTec's EpiCurve®TTwas applied for strain engineering, real-time thickness, temperature and homogeneity measurements as well as for Wafer-to-Wafer and Run-to-Run comparison to optimize the growth process. Fig. 3 demonstrate in-situ reflectance measurements of the optimized growth. This data shows a good wafer homogeneity already during the process, which is proved by XRD results in Fig. 4.

Fig. 3: In-situ reflectance data of optimized HEMT growth

Fig. 4: XRD results of the optimized HEMT growth in Fig. 3.

For further information and more measurement examples please ask info@laytec.de.

In-situ news

- Characterization of 2D materials growth 2022

- Best practices from the field: How to enhance epitaxy process performance by in-situ data

- EpiCurve® TT: AlInN composition control for III-Nitride VCSELs

- Major laser supplier chooses EpiTT FaceT for yield improvement

- EpiTT: optimizing MBE growth of InP-based quantum cascade lasers

- Plenary Talk at EWMOVPE 2019: Metrology for UV-LEDs, VCSEL and Power electronics

- EWMOVPE 2019: In-situ metrology enabling MOCVD on InP based materials on III-V on Si/SiO2 substrates for silicon photonics

- EpiX – a modular wafer mapping station for compound semiconductor research

- EpiTT Band Edge – for MBE of InP based VCSEL devices

- GaAs based edge-emitting high-power IR lasers – yield ramp-up by EpiTT FaceT

- EpiTT VCSEL – shipments to leading VCSEL manufacturer

- In-situ metrology system shipped to GaN-on-SiC customer

- Optimizing quantum cascade laser (QCL) epitaxy with EpiCurve® TTpocket satellite configuration

- In-situ metrology for VCSEL epitaxy with additional spectral reflectance sensing

- UV-C LEDs: AlGaN surface morphology monitored by 280 nm reflectance

- AIXTRON qualifies LayTec EpiNet 2016 software

- IQE equips complete fab with LayTec tools for MOCVD process monitoring

- AbsoluT 400 for temperature calibration of Pyro 400 is on the market!

- In-situ power for RF and power electronics

- Advanced in-situ analysis for UV LEDs