## State-of-the-art in-situ metrology during OMVPE in academic research and industry

Kolja Haberland *LayTec AG, Berlin, Germany*

#### Acknowledgements

Martin Zorn

JENOPTIK Diode Lab GmbH, Berlin, Germany

Arne Knauer, Frank Brunner, Andre Maaßdorf, Markus Weyers

Ferdinand-Braun-Institut, Berlin, Germany

Benjamin Buick, Claudine Groß, Christian Kaspari, Thomas Wand, Johannes K. Zettler, Thomas Zettler LayTec AG, Berlin, Germany

#### **Outline**

In-situ metrology for MOCVD – a brief sketch of historical development

Current metrology challenges

State-of-the-art metrology for VCSEL/DBR/SESAM

UV-LEDs: in-situ metrology for high Al-containing III-Ns

Summary and outlook

#### **Outline**

#### In-situ metrology for MOCVD – a brief sketch of historical development

Current metrology challenges

State-of-the-art metrology for VCSEL/DBR/SESAM

UV-LEDs: in-situ metrology for high Al-containing III-Ns

Summary and outlook

Introduction 5

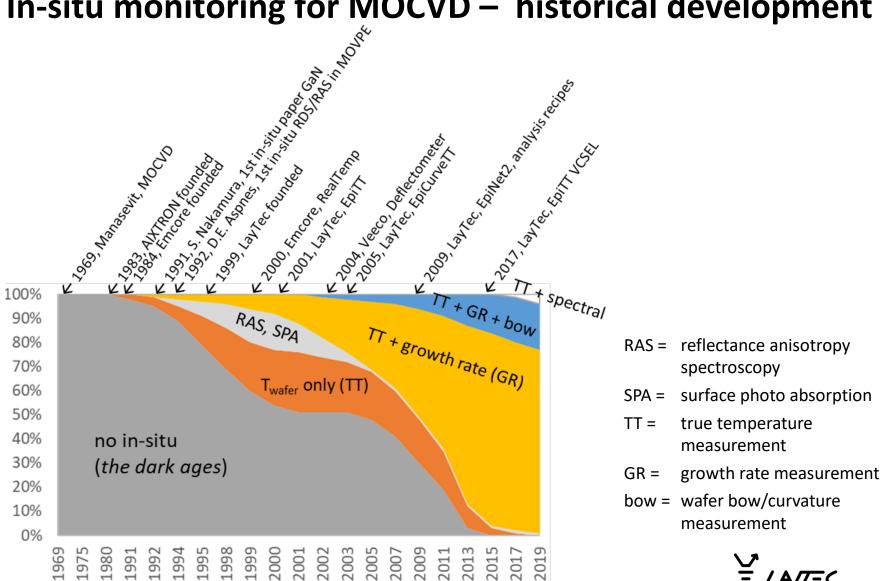

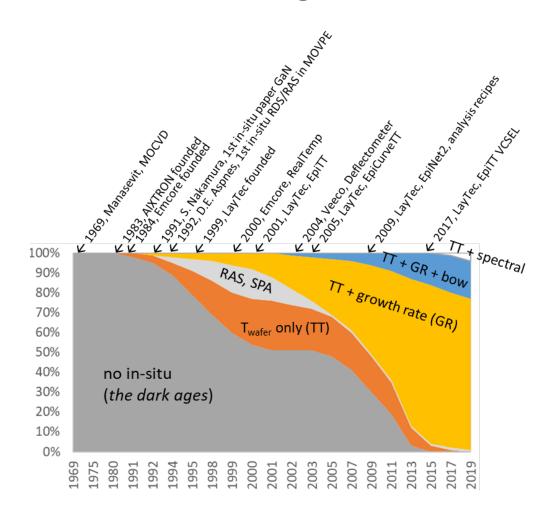

#### In-situ monitoring for MOCVD - historical development

Carl Spitzweg: "Der Alchimist" (1860)

22.08.2019

#### In-situ monitoring for MOCVD – historical development

State-of-the-art in-situ metrology during OMVPE

#### In-situ monitoring for MOCVD – historical development

Ben Stevens et al. (IQE), CSManTech, May 2019:

"All VCSEL reactors at IQE use a LayTec EpiTT ... The LayTec system also enables characterization of critical layers in a VCSEL that could not be characterized by traditional means or would require complicated modelling. Through use of analysis recipes the required analysis can be loaded into the MES before the wafers are even unloaded from the reactor."

#### **Outline**

In-situ metrology for MOCVD – a brief sketch of historical development

#### **Current metrology challenges**

State-of-the-art metrology for VCSEL/DBR/SESAM

UV-LEDs: in-situ metrology for high Al-containing III-Ns

Summary and outlook

#### **Current metrology challenges**

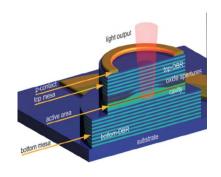

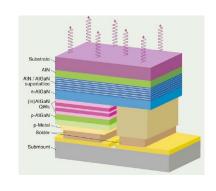

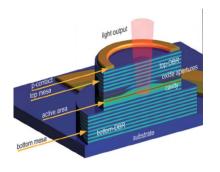

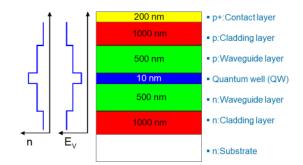

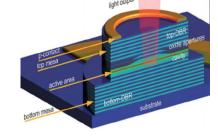

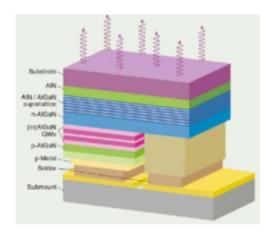

#### **VCSEL on GaAs**

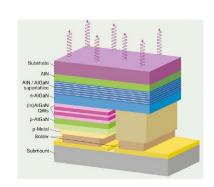

#### **UV-C LED on sapphire**

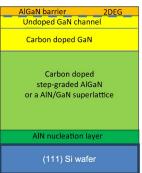

#### **GaN Power HEMT on Si**

Undoped GaN channel Carbon doped GaN Carbon doped step-graded AlGaN or a AIN/GaN superlattice AIN nucleation layer (111) Si wafer

- >100 layers; >5µm stack

- 0.1% accuracy in growth rate

- pyrometry blocked by DBR

- $x_{AlGaAs}$  for oxide aperture

- graded interfaces in DBRs

- nm-scaled layers (MQW, grading)

- 2-step epi (AlN/sapph + LED)

Large wafers + large bow

- >3µm stack

- all layers k=0

- no access to T<sub>wafer</sub>

- surface roughness  $(x_{\Delta IGaN} > 0.5)$

- High strain (AlGaN on AlN)

- nm-scaled layers (MQW, SL, EBL)

- Pyrometry: GaN is ARC on Si, 40% oscillations in emissivity

- >3μm stack, all layers k=0

- Wafer temperature during AlGaN barrier growth extremely critical

#### **Current metrology challenges**

#### VCSEL on GaAs UV-C LED on sapphire

#### GaN Power HEMT on Si

#### These three very different device structures have in common:

- >5 hours of Epi

- wafer temperature measurement is very difficult

- high-yield manufacturing is not possible without in-situ metrology

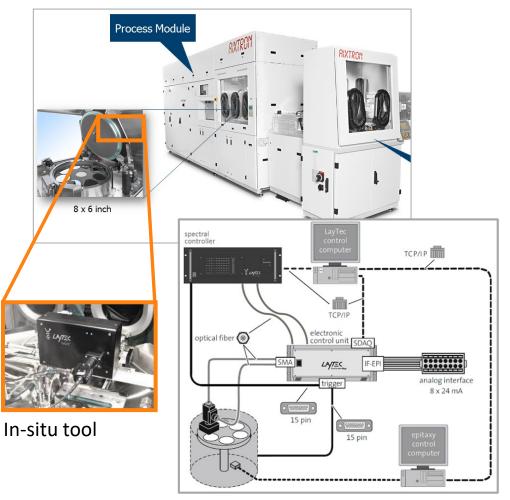

## Market leading MOCVD tool for VCSELs, GaN/Si HEMTs: AIXTRON planetary G4/G5

### This success is supported by recent advances in in-situ metrology:

- Highly precise measurement of growth rates even for very thin layers in sophisticated multi-layer structures

- Recipe controlled automated in-situ data analysis, synchronized to epi recipe, interfaced to MES

- Metrology based feed-forward of wafer temperature for satellite rotation control in long and complex device runs

#### How to measure thin layers in a multi-wafer reactor?

#### **Example: DBR interface layers in 940nm VCSEL**

6 ... 15nm graded AlGaAs, typical growth times of 12 ... 30s

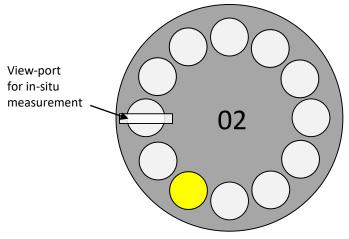

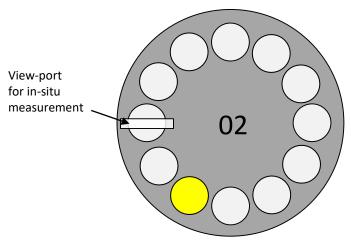

#### Typical susceptor rotation: 10 rpm, 12x3" configuration

- = Data acquisition every 6s

- = 2 data points in 12s of growth for a single wafer ... not enough!

#### How to measure thin layers in a multi-wafer reactor?

#### **Example: DBR interface layers in 940nm VCSEL**

6 ... 15nm graded AlGaAs, typical growth times of 12 ... 30s

#### Typical susceptor rotation: 10 rpm, 12x3" configuration

- = Data acquisition every 6s

- = 2 data points in 12s of growth for a single wafer ... not enough!

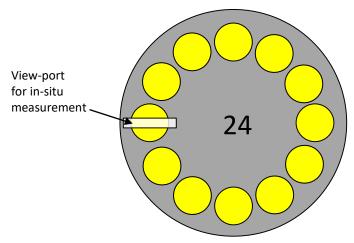

with "merged data":

- = data acquisition every 0.5s

- = 24 data points in 12s of growth

Merged dataline mode: A must for nm-scaled layers

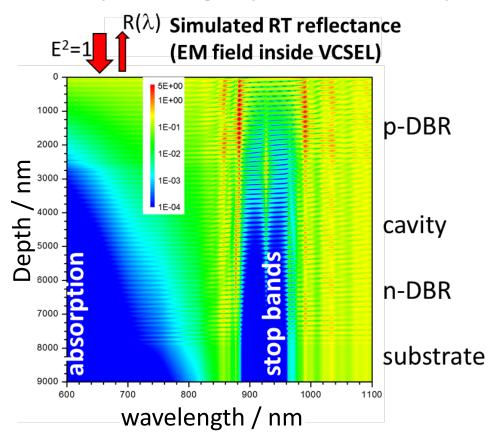

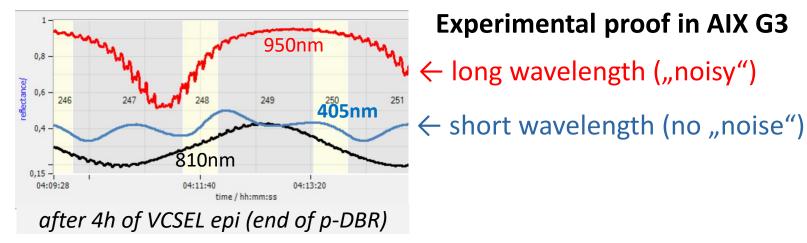

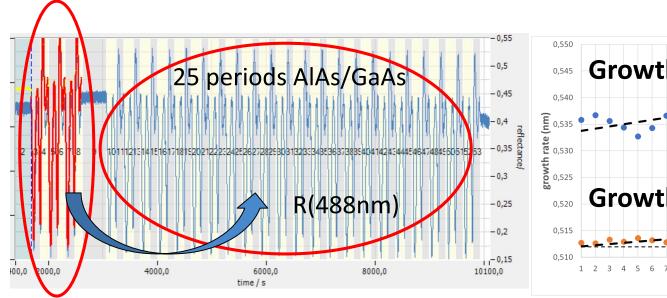

## Can we consider all wafers to be identical? Yes, if we use the right wavelength!

Analysis of light penetration depth

$\lambda > \lambda_{F0}$ :  $k^{\sim}0$

- → light penetrates all of the complex layer structure

- → tiny differences (wafer-to-wafer) accumulate

- → merged datalines are getting "noisy"

$\lambda << \lambda_{F0}$ : k>0

- → light penetrates the uppermost layers only

- → growth highly uniform

- → cutting-edge S/N of in-situ reflectance

## Wavelength selection for high-accuracy growth rate monitoring of thin layer

- Longer wavelength penetrate through whole stack = wafer-to-wafer differences accumulate

- Shorter wavelength are sensitve to uppermost layer(s) only

Data: EpiCurveTT VCSEL at Aixtron G3 11x3"/1x4" (Jenoptik)

#### Use short wavelength for growth rate monitoring of very thin layers

#### **Outline**

In-situ metrology for MOCVD – a brief sketch of historical development

Current metrology challenges

#### State-of-the-art metrology for VCSEL/DBR/SESAM

UV-LEDs: in-situ metrology for high Al-containing III-Ns

Summary and outlook

#### Current metrology challenges for VCSEL/DBR/SESAM

"Standard" requirements e.g. for **edge emitting lasers** Growth rate =  $0.500 \pm 0.005$  nm/s  $\Rightarrow$  **~±1%**

Today's advanced requirements e.g. for **VCSEL** emission wavelength (940  $\pm$  1)nm Growth rate = 0.5000  $\pm$  0.0005 nm/s  $\Rightarrow$  **~±0.1%**

• >100 layers; >5µm stack

thin layers (DBR, MQW)

#### Tasks for in-situ metrology:

- Accuracy in growth rate measurement

- integration into MOCVD for advanced process control (such as feed-forward control)

- graded interfaces in DBRs

VCSEL <u>vertical cavity surface emitting laser</u>

DBR <u>distributed Bragg mirror</u>

SESAM <u>se</u>miconductor <u>saturable</u> <u>absorber</u> <u>m</u>irrors

# growth time (~5h in total)

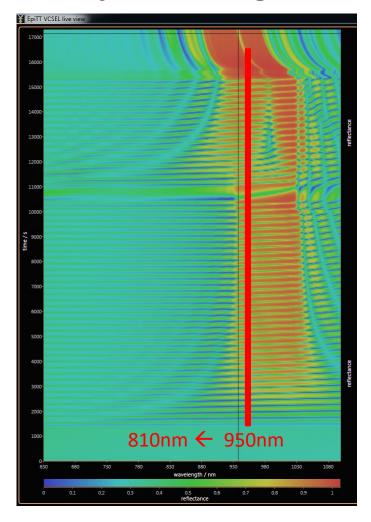

#### **Example of in-situ metrology of a VCSEL structure**

Goal: reliable prognosis of device properties by in-situ spectral reflectance

spectroscopic in-situ fingerprint

schematic layer structure

GaAs, 4"...6", at 650C...700C

600 700 800 900 1000 1100 spectral reflectance wavelength (nm)

Substrate

measured with Epi(Curve)TT VCSEL in AIXTRON G3 at Jenoptik

wafer temp wafer bow

R405nm

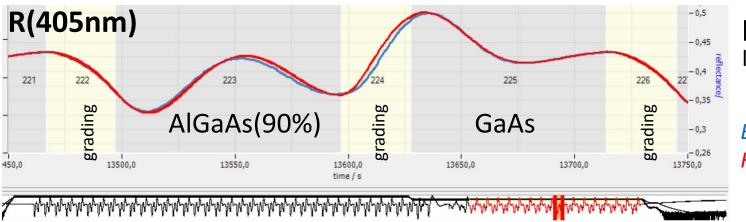

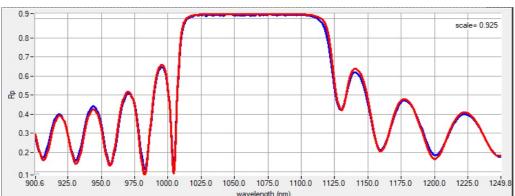

#### **Example 1: Interface grading in 940nm VCSEL DBR**

Approach:

model-based fit of measured reflectance curves for growth rate analysis

**p-DBR** lower T<sub>o</sub>

Blue: measured

Red: fitted

slow grading (30s)

Model: linear grading

#### Good agreement with linear model

#### **Example 1: Interface grading in 940nm VCSEL DBR**

Approach:

model-based fit of measured reflectance curves for growth rate analysis

**n-DBR** higher T<sub>g</sub>

Blue: measured

Red: fitted

#### Fast grading (16s)

Model: no grading

Linear change in TMG/TMA gas-flow not always leads to linear grading in x<sub>AlGaAs</sub>

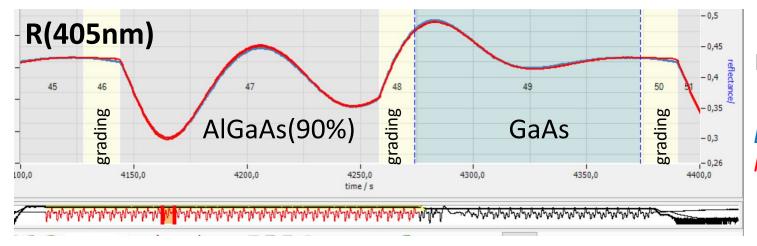

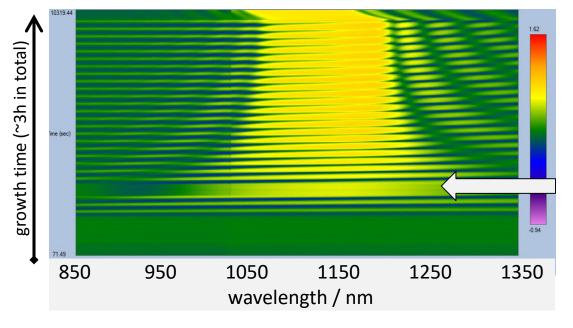

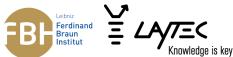

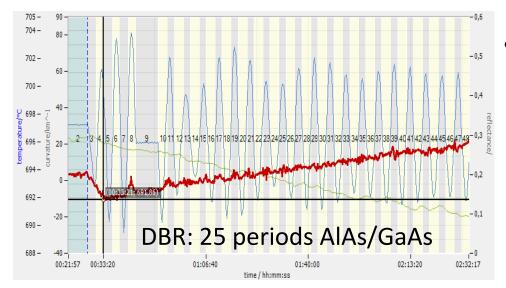

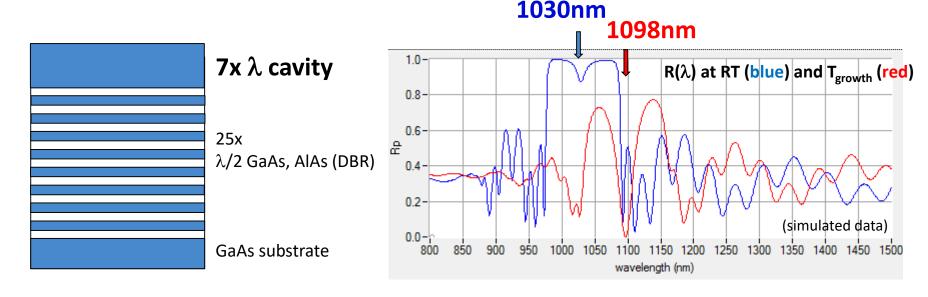

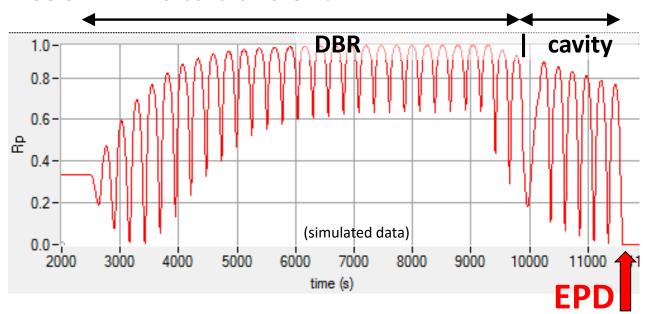

#### Example 2: SESAM (1030±1)nm – feed-forward control

- 25 pairs of GaAs/AlAs

- Full load in AIXTRON G3

- DBR Stop-Band: 990-1090nm (RT); 1030-1200nm (high T, shifted)

- Monitored by wide spectral range version (488, 633, 700-1500nm) of EpiCurveTT VCSEL

Spectral reflectance fingerprint (800-1350nm, ~3h of epi, cool-down wavelength shift is seen)

**Epi pause -** for 6-layer growth rate analysis and recipe feed-forward update

#### Example 2: SESAM (1030±1)nm – feed-forward control

- Determine growth rates of GaAs and AlAs during first 3 DBR periods

- Transmit growth rate to growth system

- Update growth times in recipe ("feed forward")

- grow remaining 22 periods

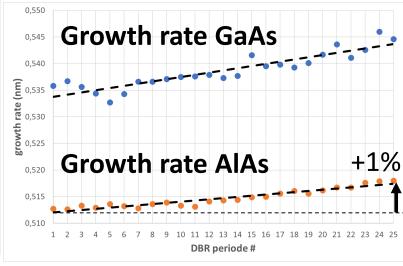

- Detailed analysis of in-situ data show linear increase of growth rates over 25 periods

- Tiny effect, but important

- Must be taken into account to achieve desired accuracy

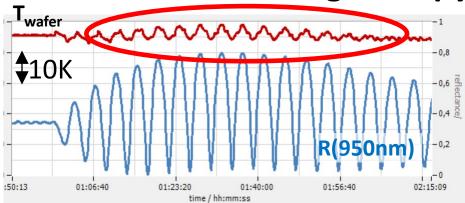

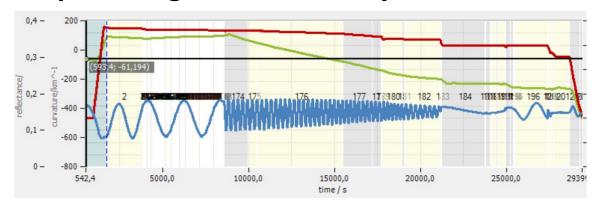

#### Example 2: SESAM (1030±1)nm – feed-forward control

## Why is growth rate slightly changing during DBR?

True Temperature

Reflectance 950nm

Curvature

- Wafer is bowing during DBR growth (compressive strain in AlAs/GaAs stack)

- Thermal emission of wafer is reduced (growing DBR is covering GaAs band-edge wavelength) → reduced cooling by radiation → wafer temperature is increasing by ~4K → AIXTRON's AFF technology needed to compensate

#### Example 2: SESAM (1030±1)nm - feed-forward control

## Why is growth rate slightly changing during DBR?

True Temperature

Reflectance 950nm

Curvature

- Wafer is bowing during DBR growth (compressive strain in AlAs/GaAs stack)

- Thermal emission of wafer is reduced (growing DBR is covering GaAs band-edge wavelength) → reduced cooling by radiation → wafer temperature is increasing by ~4K → AIXTRON's AFF technology needed to compensate

- And other effects ...

#### **Example 2: Verification by ex-situ mapping**

Mapping station EPIX combines white light reflectance and PL (multi-head mapping)

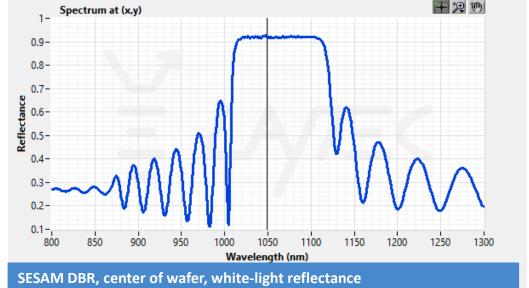

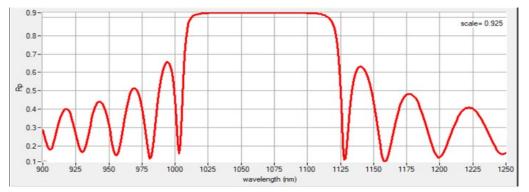

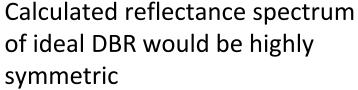

#### **Example 2: Ex-situ growth rate analysis in wafer center**

Blue: Measured DBR spectrum; asymmetric

Red: Analytic model based on insitu measured growth rates with linear increase

Growth rate<sub>GaAs</sub> = 0.4955 nm/s  $\rightarrow$  0.4990 nm/s (+1% from start of DBR to end of DBR) Growth rate<sub>AlAs</sub> = 0.5769 nm/s  $\rightarrow$  0,5839 nm/s (+1% ...)

## Excellent agreement to measured ex-situ reflectance spectrum in wafer center $\succeq \sqrt{\Delta \pi}$

#### Example 3: cavity end-point detection for 1030nm SESAM

Goal: Grow cavity with thickness of exactly 7  $\lambda$  for  $\lambda$ =1030nm

Problem: At growth temperature cavity dip and stop band are shifted

to longer wavelength

i.e. end-point control at 1030nm is useless

Solution: Select shifted wavelength of cavity resonance at T<sub>growth</sub> for end-point

detection (EPD) of cavity thickness: 1098nm

#### Example 3: cavity end-point detection for 1030nm SESAM

#### 1098nm in-situ transient

- Monitor reflectance at 1098nm

- Stop growth

when reflectance

curve goes

through 7<sup>th</sup>

minimum

- Full spectroscopic measurement allows free choice of ideal wavelength for end-point detection (EPD)

- ± 1nm accuracy in cavity dip possible by EPD

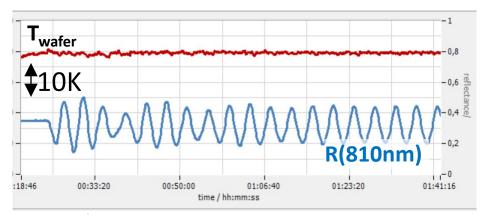

#### 940nm VCSEL – adding a 2<sup>nd</sup> pyrometry wavelength

**950nm pyro:** wafer's thermal radiation blocked by DBR ( $\varepsilon$ =1-R <20%)  $\rightarrow$  strong artifacts in T<sub>wafer</sub>

#### **Second 810nm pyrometer:**

wafer's thermal emissivity  $\varepsilon$  always >60%  $\rightarrow$  wafer temperature free of FPO artifacts

#### **Outline**

In-situ metrology for MOCVD – a brief sketch of historical development

Current metrology challenges

State-of-the-art metrology for VCSEL/DBR/SESAM

**UV-LEDs: in-situ metrology for high Al-containing III-Ns**

Summary and outlook

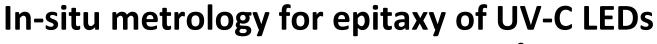

#### In-situ metrology for epitaxy of UV-C LEDs

- Growth on sapphire/AIN template

- 8h long epi; low growth rates for smoother interfaces

- two-step Epi:

- template growth in AIXTRON G3

- LED-structure in 6x2" CCS

- Total thickness: 1.5μm AlN template + 5-6μm of LED

- 85 period GaN/AlN superlattice for defect reduction

## 4-wavelength reflectance monitoring (280/405/633/950nm) for providing access to all layer thicknesses

R 405nm curvature

temperature

R 280nm curvature temperature

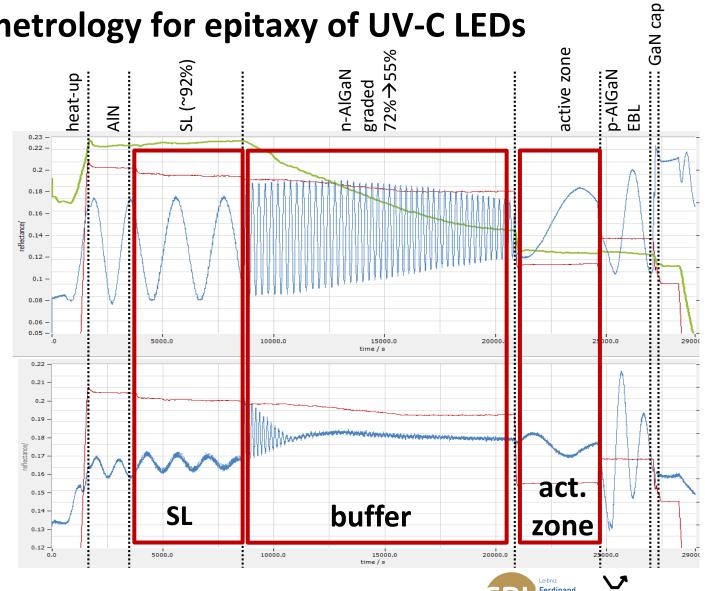

#### In-situ metrology for epitaxy of UV-C LEDs: Superlattice

- GaN/AIN SL is decisive at beginning of the UV LED epitaxy for defect reduction

- 85 periods, each single layer in the range of ~1nm

← fitting the 280nm reflection during SL growth yields SL total layer thickness of 201nm (red line)

- 280nm reflectance shows gas phase effects to the growth surface

- can be analyzed as a SPA experiment sensing the surface reconstruction changes from Al-rich → Ga-rich → Al-rich → ...

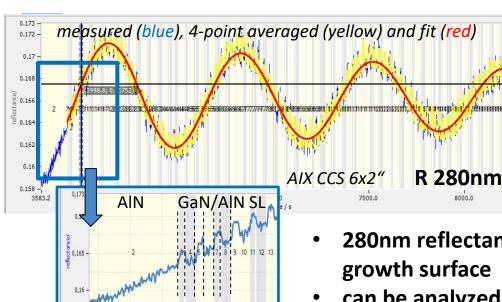

#### UV LEDs – so far no in-situ access to wafer temperature

- Fully NIR transparent substrates and layers do not allow pyrometry of wafer temperature - only pocket temperature measurement

- Molybdenum back-side coating is used for getting access to T<sub>wafer</sub> of AIN/sapph templates at start of UV-LED process

- This is work in progress ...

wafer #1

bare sapphire (dsp)

Wafer #6

AlN/sapphire template

Mo marker (center back-side)

Mafer #6

AlN/sapphire template

Mo back-side coated

#### UV LEDs – so far no in-situ access to wafer temperature

- Heating run with three different wafers

- In-situ temperature measurement

- Approach will help studying wafer temperature during UV-LED epi

sapphire wafer (dsp)

sapphire wafer (dsp)

sapphire wafer (dsp)

#### Wafer #1

bare sapphire (dsp)

$$T_{pocket} = 998$$

°C

#### Wafer #6

AlN/sapphire template

Mo marker (center back-side)

$$T_{wafer} = 985$$

°C

#### Wafer #4

AlN/sapphire template Mo back-side coated

$$T_{wafer} = 996$$

°C

- The AIN template wafer temperature at begin of UV-LED growth is 13K below pocket (graphite/SiC) temperature

- Full Mo coating of sapphire back-side improves the heat-transfer

#### **Outline**

In-situ metrology for MOCVD – a brief sketch of historical development

Current metrology challenges

State-of-the-art metrology for VCSEL/DBR/SESAM

UV-LEDs: in-situ metrology for high Al-containing III-Ns

#### Summary and outlook

#### **Summary and Outlook**

- We have developed new methods and procedures for measuring the growth rates of thin layers in highly complex device structures

- high-yield manufacturing of current cutting-edge devices can only be facilitated by close integration of in-situ metrology into the MOCVD tools

- Grading of ternary layers in DBR-like structures can be analyzed in-situ

- Ex-situ mapping of Epi uniformity achieves a new level of accuracy by feeding in the results of in-situ analysis

- Feed-forward control schemes allow endpoint detection for DBR and cavity

- Precision in in-situ reflection gives access now to surface reconstruction changes during growth

- Challenges in wafer temperature sensing for VCSELs processes have been solved

- Wafer temperature in UV LED epi remains an open issue

#### **Acknowledgement**

The authors gratefully acknowledge the financial support by the Federal Ministry of Education and Research (BMBF) of Germany in the framework of "Zwanzig20" in the project "UV Power"

The authors gratefully acknowledge the financial support by the Federal Ministry for Economic Affairs and Energy (BMWi) of Germany in the project "MOCVD 4.2"

#### Knowledge is key